### Ensuring dependability and improving performance of transactional systems deployed on multi-core architectures

Mohamed Mohamedin

Preliminary Examination Proposal submitted to the Faculty of the Virginia Polytechnic Institute and State University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Computer Engineering

Binoy Ravindran, Chair Leyla Nazhandali Mohamed Rizk Paul Plassmann Robert P. Broadwater Roberto Palmieri

November 3, 2014 Blacksburg, Virginia

Keywords: Transaction Memory, Hardware Transaction Memory (HTM), Best-efforts HTM, Transactions Partitioning, Transactions Scheduling, Transient Faults, Soft-errors, Fault-tolerance Copyright 2014, Mohamed Mohamedin Ensuring dependability and improving performance of transactional systems deployed on multi-core architectures

Mohamed Mohamedin

(ABSTRACT)

The industrial shift from single core processors to multi-core ones introduced many challenges. Among them, a program cannot get a free performance boost by just upgrading to a new hardware because new chips include more processing units but at the same (or comparable) clock speed as the previous one. In order to effectively exploit the new available hardware and thus gain performance, a program should maximize parallelism. Unfortunately, parallel programming poses several challenges, especially when synchronization is involved because parallel threads need to access the same shared data. Locks are the standard synchronization mechanism but gaining performance using locks is difficult for a non-expert programmers. A new, easier, synchronization abstraction is required and Transactional Memory (TM) is the potential candidate.

TM is a new programming paradigm that simplifies the implementation of synchronization. The programmer just defines atomic parts of the code and the underlying TM system handles the required synchronization. In the past decade, TM researchers worked extensively to improve TM-based systems. Most of the work has been dedicated to Software TM (STM) as it does not requires special transactional hardware supports. Very recently (in the past two years), those hardware support have become commercially available in commodity processors. Hardware TM (HTM) provides the best performance of any TM-based systems, but current HTM systems are best-effort, thus transactions are not guaranteed to commit. In fact, HTM transactions are limited in size and time as well as prone to livelock at high contention levels.

Another challenge facing multi-core architectures is dependability. In the hardware design, factors such as increasing number of components on the same chip, reducing transistor's size, and reducing the operating voltage cooperate to increase the rate of soft-errors. Soft-errors are transient faults that can randomly flip registers and memory (likely cache) bits. Multi-core architectures meet all aforementioned factors, thus they are prone to soft-errors.

In this dissertation, we tackle the performance and dependability challenges of multi-core architectures by providing two solutions for increasing performance using HTM (i.e., PART-HTM and OCTONAUTS), and two solutions for solving soft-errors (i.e., SHIELD and SOFTX).

PART-HTM is an innovative Hybrid TM system that alleviates HTM resource limitation. A large transaction is partitioned into smaller partitions that fit in HTM. Thus, large transactions can achieve high performance by exploiting HTM speed. Transaction partitioning poses many correctness challenges which are handled by PART-HTM. Results in benchmarks where transactions are mostly aborted for resource failures confirmed PART-HTM effectiveness. In those benchmarks PART-HTM is the best, gaining up to 74%.

OCTONAUTS tackles the live-lock problem of HTM at high contention level. HTM lacks of advanced contention management (CM) policies. OCTONAUTS is an HTM-aware scheduler that orchestrates conflicting transactions. It uses a priori knowledge of transactions' working-set to prevent the activation of conflicting transactions, simultaneously. OCTONAUTS also accommodates both HTM and STM with minimal overhead by exploiting adaptivity. Based on the transaction's size, time, and irrevocable calls (e.g., system call) OCTONAUTS selects the best path among HTM, STM, or global locking. Results show performance improvement

when OCTONAUTS is deployed in comparison with pure HTM with falling back to global locking.

SHIELD is a fault-tolerant system for transactional application using state-machine replication (SMR). It is optimized for centralized multi-core architectures specially message-passing based ones. It includes an efficient network layer for ordering transactional requests with optimistic delivery support. The other main component of SHIELD is the concurrency control. It supports concurrent execution of transactional requests while forcing the network layer order. SHIELD is also able to speculatively start transactions as soon as the request is optimistically delivered. SHIELD's results show limited overhead in comparison with non-faulttolerant transactional systems and improvement over other non-optimized SMR approaches.

SOFTX is a low-invasive protocol for supporting execution of transactional applications relying on speculative processing and dedicated committer threads. Upon starting a transaction, SOFTX forks a number of threads running the same transaction, independently. The commit phase is handled by dedicated threads for optimizing synchronization's overhead. Results reveal better performance than classical replication-based fault-tolerant systems and limited overhead with respect to non fault-tolerant protocols. In comparison with SHIELD, SOFTX does not requires computational resource partitioning nor requests ordering but it has smaller fault coverage.

Our first major post-preliminary research goal is to develop a contention manager for HTM that works based on online information without a priori knowledge of the transaction's accesses. Dropping this knowledge increases the CM accuracy and allows more concurrency. The challenge posed by this goal is to allow the sharing of online information without introducing additional aborts due to the nature of HTM conflict resolution. Our second goal is to add advanced nesting capabilities (i.e., closed and open nesting) to HTM. HTM supports basic flat nesting only and it is limited to 7 levels only. Advanced nesting is known to improve the performance. For example, in closed nesting, aborting a child transaction does not abort the parent transaction. Our third goal is to build a comprehensive framework for Hybrid TM algorithms. In fact, analyzing the current literature of Hybrid TM algorithms, we can identify several common building blocks used to build those algorithm. Our proposed framework makes the implementation of hybrid TM algorithms easy. It aims for helping the research community in developing more hybrid TM algorithms, deploying extensive comparison studies and allowing the composability of different hybrid TM algorithms according to the transaction's characteristics.

This work is supported in part by US National Science Foundation under grants CNS 0915895, CNS 1116190, CNS 1130180, and CNS 1217385.

# Contents

| 1                              | Intr         | roduction                                             | 1  |  |  |  |

|--------------------------------|--------------|-------------------------------------------------------|----|--|--|--|

|                                | 1.1          | Summary of Current Research Contributions             | 3  |  |  |  |

|                                |              | 1.1.1 Improving Multi-core Performance Exploiting HTM | 3  |  |  |  |

|                                |              | 1.1.2 Ensuing multi-core Dependability                | 5  |  |  |  |

|                                | 1.2          | Summary of Proposed Post-Prelim Work                  | 7  |  |  |  |

|                                | 1.3          | Proposal Outline                                      | 8  |  |  |  |

| <b>2</b>                       | Related Work |                                                       | 9  |  |  |  |

|                                | 2.1          | Performance Improvement Using HTM                     | 9  |  |  |  |

|                                | 2.2          | Transactional Memory Scheduling                       | 11 |  |  |  |

|                                | 2.3          | Dependability                                         | 12 |  |  |  |

| 3                              | Background 1 |                                                       |    |  |  |  |

|                                | 3.1          | Parallel Programming                                  | 15 |  |  |  |

|                                | 3.2          | Transactional Memory                                  | 16 |  |  |  |

|                                |              | 3.2.1 TM Design Classification                        | 16 |  |  |  |

|                                | 3.3          | Intel's HTM                                           | 18 |  |  |  |

|                                | 3.4          | Soft-errors                                           | 19 |  |  |  |

| 3.5 Fault tolerance techniques |              | Fault tolerance techniques                            | 20 |  |  |  |

|                                |              | 3.5.1 Checkpointing                                   | 20 |  |  |  |

|                                |              | 3.5.2 Encoding                                        | 21 |  |  |  |

|                                |              | 3.5.3 Assertions/Invariants                           | 21 |  |  |  |

|          |     | 3.5.4                 | Replication                                    | . 21 |  |  |  |  |

|----------|-----|-----------------------|------------------------------------------------|------|--|--|--|--|

| 4        | Par | art-HTM 2             |                                                |      |  |  |  |  |

|          | 4.1 | Proble                | em Statement                                   | . 23 |  |  |  |  |

|          |     | 4.1.1                 | Intel's HTM Limitations                        | . 26 |  |  |  |  |

|          | 4.2 | Algori                | thm Design                                     | . 26 |  |  |  |  |

|          | 4.3 | 4.3 Algorithm Details |                                                |      |  |  |  |  |

|          |     | 4.3.1                 | Protocol Meta-data                             | . 31 |  |  |  |  |

|          |     | 4.3.2                 | Begin Operation and Transaction's Partitioning | . 31 |  |  |  |  |

|          |     | 4.3.3                 | Transactional Read Operation                   | . 32 |  |  |  |  |

|          |     | 4.3.4                 | Transactional Write Operation                  | . 32 |  |  |  |  |

|          |     | 4.3.5                 | Validation                                     | . 33 |  |  |  |  |

|          |     | 4.3.6                 | Commit Operations                              | . 36 |  |  |  |  |

|          |     | 4.3.7                 | Aborting a Transaction                         | . 36 |  |  |  |  |

|          | 4.4 | Compa                 | atibility with other HTM processors            | . 36 |  |  |  |  |

|          | 4.5 | 5 Correctness         |                                                |      |  |  |  |  |

|          | 4.6 | Evalua                | ation                                          | . 38 |  |  |  |  |

| <b>5</b> | Oct | Octonauts             |                                                |      |  |  |  |  |

|          | 5.1 | Proble                | em Statement                                   | . 43 |  |  |  |  |

|          | 5.2 | Algori                | thm Design                                     | . 45 |  |  |  |  |

|          | 5.3 | Algori                | thm Details                                    | . 46 |  |  |  |  |

|          |     | 5.3.1                 | Reducing Conflicts via Scheduling              | . 46 |  |  |  |  |

|          |     | 5.3.2                 | HTM-aware Scheduling                           | . 48 |  |  |  |  |

|          |     | 5.3.3                 | Transactions Analysis                          | . 49 |  |  |  |  |

|          |     | 5.3.4                 | Adaptive Scheduling                            | . 50 |  |  |  |  |

|          | 5.4 | Evalua                | ation                                          | . 51 |  |  |  |  |

|          |     | 5.4.1                 | Bank                                           | . 51 |  |  |  |  |

|          |     | 5.4.2                 | TPC-C                                          | . 52 |  |  |  |  |

| 6 | Shie | Shield                                        |                                        | 54 |  |

|---|------|-----------------------------------------------|----------------------------------------|----|--|

|   | 6.1  | Proble                                        | em Statement                           | 54 |  |

|   | 6.2  | .2 Is Byzantine Fault Tolerance the Solution? |                                        |    |  |

|   | 6.3  | Syster                                        | n Model and Assumptions                | 58 |  |

|   | 6.4  | Fault                                         | Model                                  | 58 |  |

|   | 6.5  | Shiel                                         | D Design                               | 59 |  |

|   |      | 6.5.1                                         | Overview                               | 59 |  |

|   |      | 6.5.2                                         | Limitations                            | 61 |  |

|   | 6.6  | Netwo                                         | ork Layer                              | 61 |  |

|   |      | 6.6.1                                         | Tolerating CPU-tfaults                 | 63 |  |

|   | 6.7  | Replic                                        | ea Concurrency Control                 | 64 |  |

|   | 6.8  | Evalua                                        | ation                                  | 69 |  |

|   |      | 6.8.1                                         | Tilera TILE-Gx family                  | 69 |  |

|   |      | 6.8.2                                         | x86 Architecture                       | 74 |  |

| 7 | Soft | $\mathbf{X}$                                  |                                        | 77 |  |

|   | 7.1  | Proble                                        | em Statement                           | 77 |  |

|   | 7.2  | Assum                                         | nptions and Applicability              | 80 |  |

|   | 7.3  | Design                                        | n and Implementation                   | 81 |  |

|   | 7.4  | Exper                                         | imental Results                        | 86 |  |

|   |      | 7.4.1                                         | Shared-bus architecture                | 89 |  |

|   |      | 7.4.2                                         | Message-passing architecture           | 90 |  |

| 8 | Cor  | clusio                                        | ns                                     | 91 |  |

|   | 8.1  | Propo                                         | sed Post-Prelim Work                   | 92 |  |

|   |      | 8.1.1                                         | HTM Advanced Online Contention Manager | 92 |  |

|   |      | 8.1.2                                         | HTM Advanced Nesting Support           | 93 |  |

|   |      | 8.1.3                                         | Hybrid TM Framework                    | 94 |  |

# List of Figures

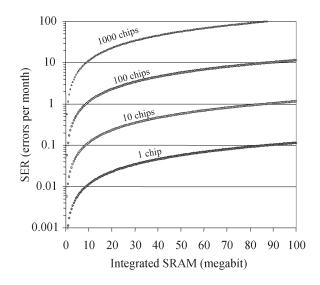

| 3.1 | Relation between number of components on the same chip and soft-errors rate. (Figure from [11])                      | 19 |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

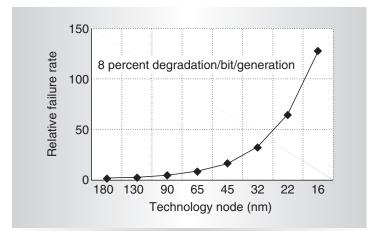

| 3.2 | Relation between transistor size and soft-errors rate. (Figure from [16]) $\ .$ .                                    | 20 |

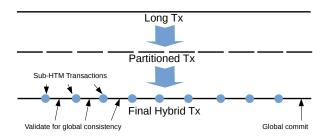

| 4.1 | PART-HTM's Basic Idea.                                                                                               | 27 |

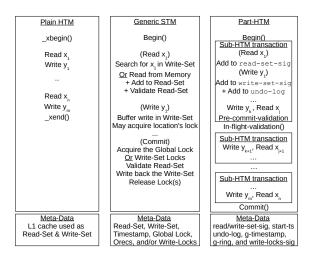

| 4.2 | Comparison between HTM, STM, and PART-HTM.                                                                           | 29 |

| 4.3 | PART-HTM's pseudo-code.                                                                                              | 30 |

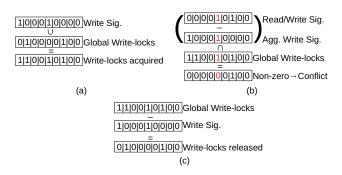

| 4.4 | Acquiring write-locks (a). Detecting intermediate reads or potential over-<br>writes (b). Releasing write-locks (c). | 34 |

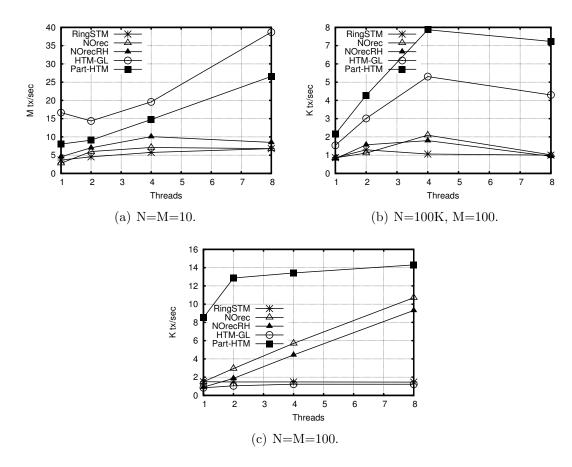

| 4.5 | Throughput using N-Reads M-Writes benchmark and disjoint accesses                                                    | 39 |

| 4.6 | Throughput using Linked-List                                                                                         | 40 |

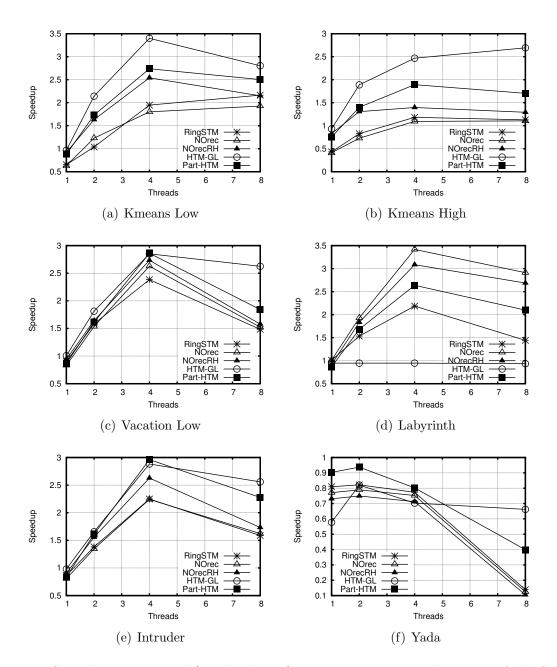

| 4.7 | Speed-up over serial (single-thread) execution using applications of the STAMP Benchmark.                            | 42 |

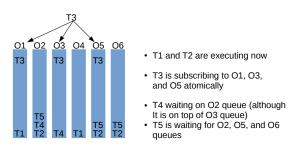

| 5.1 | Scheduling transactions.                                                                                             | 46 |

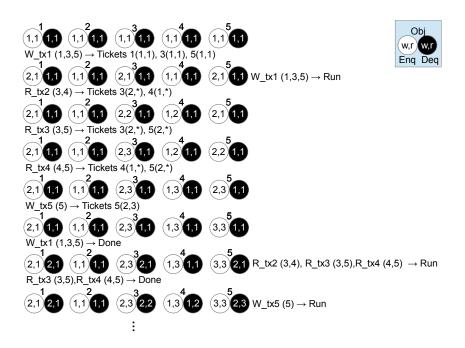

| 5.2 | Readers-Writers ticketing technique                                                                                  | 47 |

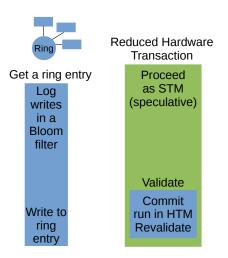

| 5.3 | HTM-STM communication.                                                                                               | 48 |

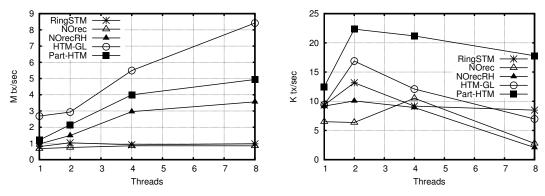

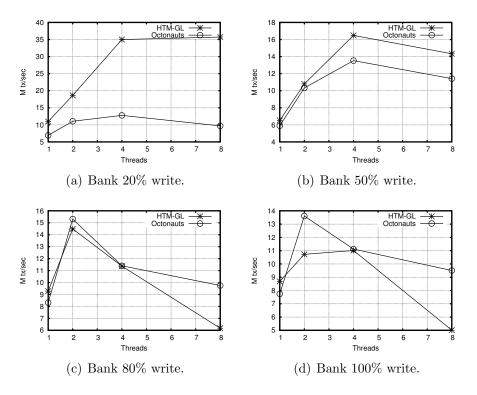

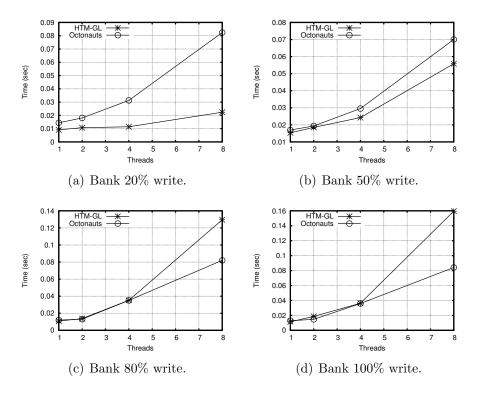

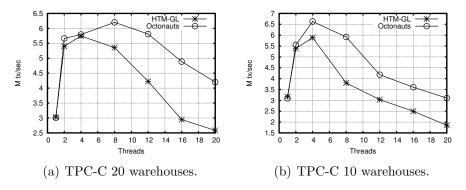

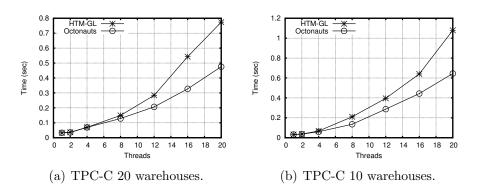

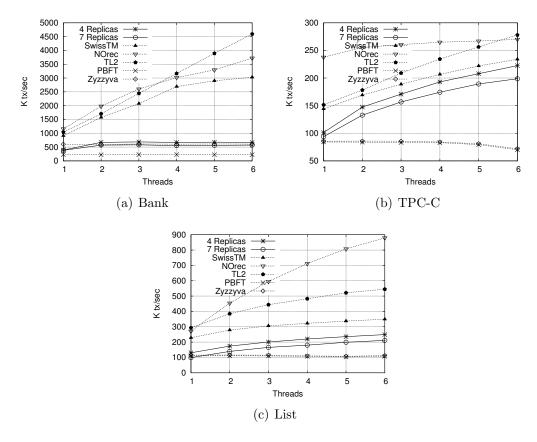

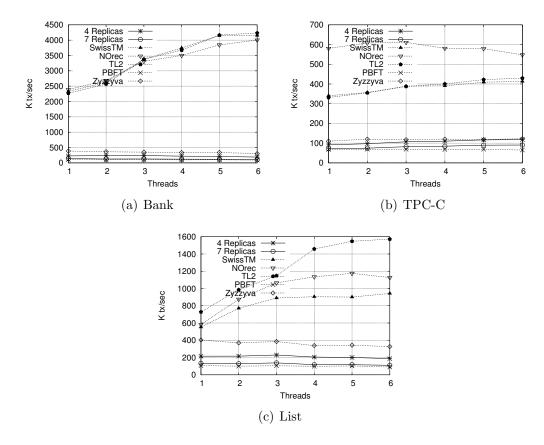

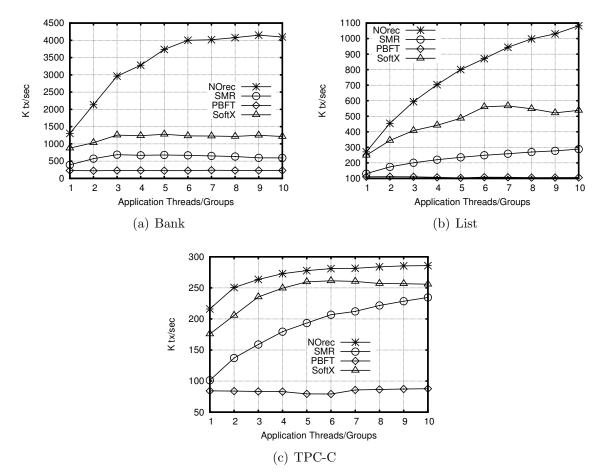

| 5.4 | Throughput using Bank benchmark.                                                                                     | 50 |

| 5.5 | Execution time using Bank benchmark (lower is better).                                                               | 51 |

| 5.6 | Throughput using TPC-C benchmark.                                                                                    | 52 |

| 5.7 | Execution time using TPC-C benchmark                                                                                 | 52 |

| 6.1 | System, replica and software architecture.                                                                           | 56 |

| 6.2 | Network Layer Protocol (Application side)                                                                            | 63 |

| 6.3  | Network Layer Protocol (Replica side)                               | 64 |

|------|---------------------------------------------------------------------|----|

| 6.4  | Transaction's read procedure.                                       | 67 |

| 6.5  | Transaction's write procedure.                                      | 68 |

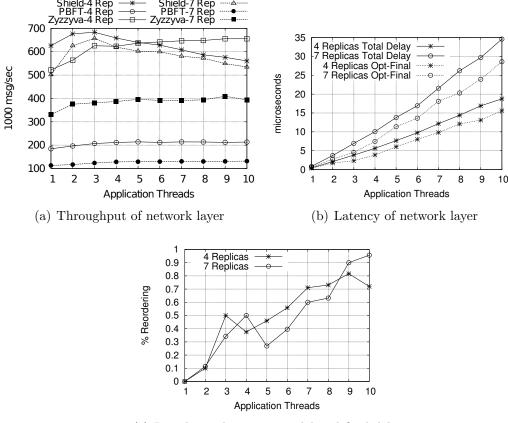

| 6.6  | Performance of network layer on Tilera                              | 69 |

| 6.7  | Transactional throughput of SHIELD on Tilera.                       | 72 |

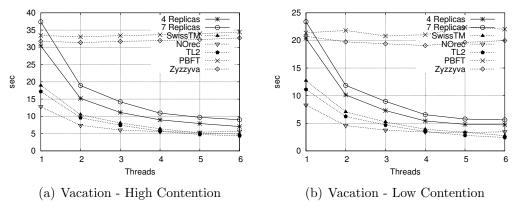

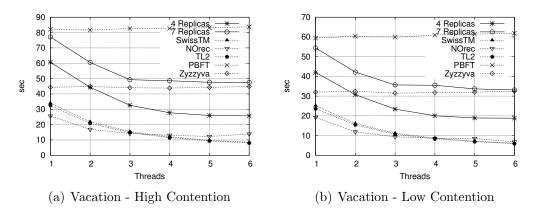

| 6.8  | Vacation execution time on Tilera.                                  | 73 |

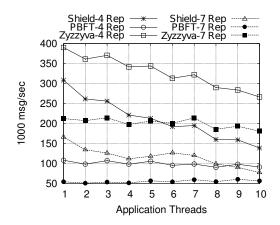

| 6.9  | Network layer throughput on x86                                     | 74 |

| 6.10 | Transactional throughput of Shield on x86                           | 75 |

| 6.11 | Vacation execution time on x86                                      | 76 |

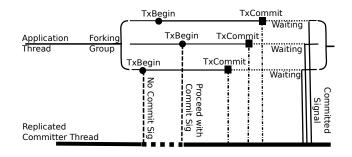

| 7.1  | Processing transaction with SOFTX.                                  | 83 |

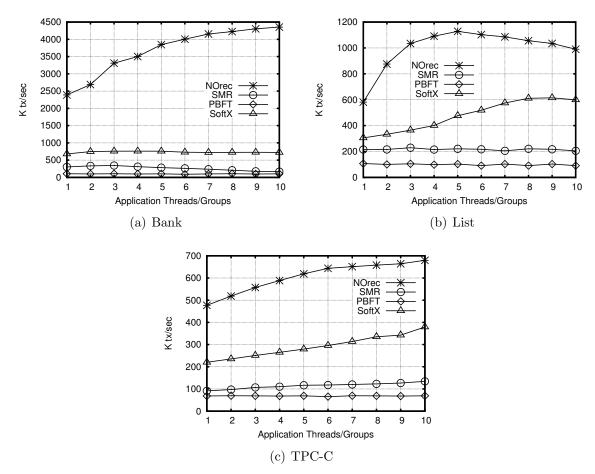

| 7.2  | Transactional throughput of SOFTX on x86                            | 85 |

| 7.3  | Transactional throughput of SOFTX on Tilera                         | 87 |

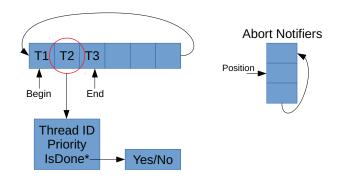

| 8.1  | The proposed object's circular buffer meta data and abort notifiers | 93 |

# List of Tables

## Chapter 1

## Introduction

Multi-core architectures are the current trend. They are everywhere from super computers to mobile devices. The future trend is to increase the number of cores in each CPU and enhance the communication speed between cores as well as the number of CPU sockets. Without exploiting parallelism, a program cannot gain more performance when deployed on an upgraded hardware, which includes more cores with a clock speed that is similar to the previous hardware. Unfortunately, multi-core programming is an advanced topic, often suited only for expert programmers. Therefore, in order to gain more performance from current and emerging multi-core systems, we need an easy, transparent and efficient mechanism for programming them, a mechanism that allows more programmer to do concurrent programming efficiently and correctly. An effective abstraction is Transactional Memory (TM) [54, 51, 99, 63, 35]. TM programming model is as easy as coarse-grained locking. The entire critical section is marked as a transaction instead of guarding it with a single lock. Coarse-grained locking serializes all threads accessing the same critical section and it does not allow concurrent access. On the contrary, TM allows more concurrency. As long as transactions are not conflicting, they are allowed to run and commit concurrently. Two transactions conflict only when they access the same object and one of the operation is a write. TM also guarantees atomicity, consistency, and isolation. Thus, a transaction is executed all or nothing, always observing a consistent state, and it works in isolation from other transactions.

In terms of performance, TM is prone to have comparable performance to fine-grain locking, which in principle uses the minimal number of locks needed for preserving the correctness of the program. Unfortunately, fine-grain locking cannot be composable, e.g., two atomic blocks implemented using fine-grain locking cannot be naively put together in a single transaction because the resulting transaction is likely not atomic and isolated from other concurrent accesses. The TM's abstraction solves this problem, thus providing composability.

TMs are classified as *software* (STM) [38, 33], which can be executed without any transactional hardware support, *hardware* (HTM) [54, 51, 26], which exploits specific hardware facilities, and hybrid (HyTM) [63, 35], which mixes both HTM and STM.

TM has been studied extensively for the past decade [54, 51, 99, 55, 105, 93, 61, 53, 17, 101, 39, 38, 33]. Most of the research efforts were directed towards STM. STM systems run on any hardware and do not requires any transactional hardware support. On the contrary, commercial Hardware TM support was lately introduced in the past two years. Before that, all HTM research was done on simulators or very specialized hardware. On the other hand, STM research continued to cover more scenarios (e.g., performance tuning, contention management, scheduling, nesting, semantic aware STM). STM gained industry traction starting by Intel C++ STM compiler [57], followed by including TM constructs in C++11/C1X new standards, and finally adopted by the famous GCC compiler starting from version 4.7.

Hardware TM is recently available commercially now in commodity CPUs (i.e., Intel Haswell) and HPC (i.e., IBM Blue Gene/Q and IBM Power 8 [18]). Both Intel's and IBM's HTMs are *best-efforts* HTM: a transaction is not guaranteed to commit, even if it runs alone. A fallback path must be provided by the programmer for transactions that fail in HTM. The default fallback path is to acquire a global lock. But, more advanced techniques have been recently introduced to improve HTM performance and overcome HTM limitations [19, 3, 20, 75, 76, 41, 2]. Unfortunately, the well studies STM techniques cannot be ported directly to HTM or Hybrid TM. With many high performance STM algorithms (e.g., TL2), the performance is highly degraded compared to both plain HTM and plain STM [94, 75]. Thus, Hybrid TM algorithms requires careful design to balance the added overhead on both HTM and STM components.

Another issue with multi-core architectures is dependability. Multi-core architectures manufacturing trend is to add more cores on the same chip and reduce transistors size. These two factors (i.e., smaller transactions and more components on the same chip) are shown to be responsible for an increased rate of soft-errors [16, 11]. Soft-errors are transient faults that may happen anytime during application execution. They are caused by physical phenomena [11], e.g., cosmic particle strikes or electric noise, which cannot be directly managed by application designers or administrators. As a result, when a soft-error occurs, the hardware is not affected by interruption, but applications may crash or behave incorrectly. A soft error can cause a single bit in a CPU register to flip (i.e., residual charge inverting the state of a transistor). Most of the time, such an event is likely to be unnoticed by applications because they do not use that value (e.g., unused register). However, sometimes, the register can contain an instruction pointer or a memory pointer. In those cases, the application behavior can be unexpected.

As a result, multi-core architectures are prone to transient faults (e.g., soft-errors), thus applications with dependability requirements (i.e., fault-tolerance, availability and reliability) cannot be directly migrated into a multi-core architecture without providing them with a mechanism for addressing transient faults. Current fault tolerance techniques are not optimized for multi-core architectures, whereas they are designed for distributed systems where

communication delays allow for special types of optimizations. Communication delays in multi-core architectures are very limited. Other fault tolerance techniques are designed to guarantee data correctness without liveness (e.g., checkpointing and high availability).

Motivated by these observations, this thesis focuses on two aspects: improving multi-core performance by exploiting best-efforts HTM while overcoming its limitations; providing multi-core dependability by developing fault tolerant software layer, which is optimized for multi-core architectures.

### **1.1 Summary of Current Research Contributions**

#### 1.1.1 Improving Multi-core Performance Exploiting HTM

Gaining more performance from multi-core architectures requires exploiting concurrency and parallelism. However, having multiple threads that act simultaneously usually means synchronizing their accesses once they want to operate on the same data, otherwise the program's correctness is broken. Coarse-grained locking is easy to program but serialize access to shared data. Hence, it reduces concurrency which affects performance and cannot scale. Fine-grained locking is used to allow more concurrency by fine tuning locking. It uses multiple locks and splits large critical section into smaller fine tuned ones. Fine-grained locking is algorithm based and cannot be generalized. In addition, only expert programmers can handle it due to its complexity. Non-expert programmers can easily face deadlocks, livelocks, lockconvoying, and/or priority inversion. Perhaps, the most significant limitation of lock-based synchronization is that it is not composable. For example, we have a concurrent lock-based hash table. It has two atomic operations (put and remove). Now, we have two of this hash table and we want to atomically remove an entry from one table and add it to the other. Composing add and remove operations cannot guarantee the atomicity of composition. Lock-free synchronization is based on atomic instruction (e.g., compare-andswap (CAS)) but, as the fine-grain locking technique, it is algorithmic specific and hard to generalize.

Transactional Memory (TM) simplify parallel programming to the level of coarse-grained locking while achieving fine-grained locking performance. With the introduction of commercial HTM support, TM performance can finally exceed fine-grained locking performance. Thus, making TM programming model more appealing. The problem with current HTM support by Intel and IBM is being best-efforts HTM, thus a transaction is not guaranteed to commit even if it runs alone with no contention. Also, an HTM transaction has resource limitations (e.g., hardware buffer size, hardware interrupts) which forces the transaction to abort in HTM. Thus, an HTM transaction is limited in size and time. The space limitation is due to limited hardware transactional buffer size, while time limitation is due to the clock tick hardware interrupt that is used by the operating system's scheduler. A fallback path is required by best-efforts HTM to guarantee progress. The default fallback path is to use a global lock (GL-software path). GL-software path limits concurrency and does not scale for transactions that do not fit in HTM due to resource limitation as it is simply serializing them.

**Part-HTM**. To tackle best-efforts HTM resource limitations, we propose PART-HTM, an innovative transaction processing scheme, which prevents those transactions that cannot be executed as HTM due to space and/or time limitation to fall back to the GL-software path, and commit them still exploiting the advantages of HTM. As a result, PART-HTM limits the transactions executed as GL-software path to those that retry indefinitely in hardware (e.g., due to extreme conflicting workloads), or that require the execution of irrevocable operations (e.g., like system calls), which are not supported in HTM.

PART-HTM's core idea is to first run transactions as HTM and, for those that abort due to resource limitations, a partitioning scheme is adopted to divide the original transaction into multiple, thus smaller, HTM transactions (called sub-HTM), which can be easily committed. However, when a sub-HTM transaction commits, its objects are immediately made visible to others and this inevitably jeopardizes the isolation guarantees of the original transaction. We solve this problem by means of a software framework that prevents other transactions from accessing objects committed to the shared memory by sub-HTM transactions. This framework is designed to be minimal and low overhead: a heavy instrumentation would annul the advantages of HTM, falling back into the drawbacks of adopting a pure STM implementation. PART-HTM uses locks, to isolate new objects written by sub-HTM transactions from others, and a slight instrumentation of read/write operations using cache-aligned signature-based structures, to keep track of accessed objects. In addition, a software validation is performed to serialize all sub-HTM transactions in a single point in time.

With this limited overhead, PART-HTM gives performance close to pure HTM transactions, in scenarios where HTM transactions are likely to commit without falling back to the software path, and close to pure STM transactions, where HTM transactions repeatedly fail. This latter goal is reached through the exploitation of sub-HTM transactions, which are indeed faster than any instrumented software transactions. In other words, PART-HTM's performance gains from HTM's advantages even for those transactions that are not originally suited for HTM resource failures. Given that, PART-HTM does not aim at either improving performance of those transactions that are systematically committed as HTM, or facing the challenge of minimizing conflicts of running transactions. PART-HTM has a twofold purpose: it commits transactions that are hard to commit as HTM due to resource failures without falling back to the GL-software path but still exploiting the effectiveness of HTM (leveraging sub-HTM transactions); and it represents in most of the cases an effective trade-off between STM and HTM transactions.

PART-HTM ensures serializability [1], the well-known consistency criterion for transaction processing, and, relying on the HTM protection mechanism (i.e., sandboxing), it guarantees that aborted transactions cannot propagate corrupted execution to the software framework.

**Octonauts**. PART-HTM tackled the problem of HTM resource limitations, but another problem afflicts TM in general, which is handling efficiently conflicts. At high contention levels, transactions keep aborting with each other and can lead to livelock situation. In STM systems, this problem is solved by using a contention manager or a scheduler. A contention manager is consulted whenever two transactions are conflicting. And based on the contention manager rules, the conflict is resolved. For example, a conflict resolution rule can be "older transaction wins". In that case, old transactions are prioritized over newer ones. Thus, old transactions will not starve. A scheduler on the other hand uses information about each transaction and schedule transactions such that conflicting transactions are not scheduled concurrently.

Current Intel HTM implementation has a simple conflict resolution rule where the thread that detect the conflict aborts. This rule does not prevent starvation. In addition, there is no way for the programmer to define conflict resolution rules. Simply, in high contention scenarios, an HTM transaction will face several aborts and then fall back to global locking. Falling back to global locking limits the system's concurrency level and serializes non conflicting transactions, which results in bad performance and scalability.

In order to tackle this problem, we propose OCTONAUTS, an HTM-aware scheduler which aims at reducing conflicts between transactions and providing an efficient STM fallback path. OCTONAUTS basic idea is to use queues that guard shared objects. A transaction first publishes its potential objects that will be accessed during the transaction (working set). That information is provided by the programmer or by a static analysis of the program. Before starting a transaction, the thread subscribes to each object queue atomically. Then, when it reaches the top of all subscribed queues, it starts executing the transaction. Finally, it is dequeued from those queues, allowing the following threads to proceed with their own transactions. Large transactions that cannot fit in HTM are started directly in STM with commit phase as a reduced hardware transaction (RHT) [76]. In order to allow HTM and STM to run concurrently, HTM transactions runs in two modes. First mode is plain HTM, where a transaction runs as a standard HTM transaction. The second mode is initiated once an STM transaction is required to execute. In the second mode, a lightweight instrumentation is used to let the concurrent STMs know about executing HTM transactions. We focused on making this instrumentation transparent to HTM transactions. HTM transactions are not aware of concurrent STM transactions and use objects signature to notify STM transactions about written objects. STM uses concurrent HTM write signatures to determine if its read-set is still consistent. This technique does not introduce false conflicts in HTM transactions. If a transaction is irrevocable, it is stated directly using global locking.

#### 1.1.2 Ensuing multi-core Dependability

In multi-core dependability, we focused on transactional applications. Transactional applications state can only be accessed via transactions. The application state must remain

consistent and fault tolerant. In addition to safety requirements, transactional application must maintain liveness also. In order to achieve these goals we present SHIELD and SOFTX.

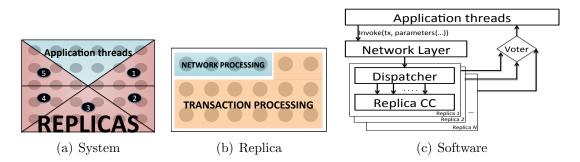

**Shield.** SHIELD is an optimized state-machine replication (SMR) for multi-core architectures. It exploit the emerging message-passing hardware and the local synchronized cycle counter register. SHIELD has two main components, the network layer and the concurrency control. SHIELD's key idea is to partition the available resources, and run the application's transactions on all the partitions in parallel, according to the state-machine replication paradigm. As in state-machine replication, transaction requests are wrapped into network messages that the application submits to an ordering layer. This layer implements the specification of *Optimistic Atomic Broadcast* [59] (OAB), and ensures a global serialization order (GSO) among partitions. Each partition is thus notified with the same sequence of transactions and is able to process those transactions independently from the other partitions. Objects accessed by transactions are fully replicated so that each partition can access its local copy, avoiding further communications. Transactions are processed according to the GSO. Additionally, we use a *voter* for collecting the outcome of transactions and delivering the common response (i.e., majority of the replies) to the application. If one or more replies differ, actions are triggered to restore the consistent status of data in those faulty partitions. Assuming the majority of partitions are correct (i.e., non-faulty), the voter just selects the proper transaction reply to deliver back to the application thread and uses the collected replies that differ from the one delivered to the application for identifying faulty partitions.

With SHIELD, we focus on reducing network protocol latency and optimistically deliver requests in one communication step. We also focused on increasing concurrency in request processing to maximize multicore systems' utilization and reducing ordering layer latency by optimistically executing requests while the final order is established.

SHIELD makes the following contributions: i) A new network protocol for ordering requests, that is optimized for centralized systems and that supports optimistic delivery by exploiting the local synchronized cycle counter register; ii) An innovative concurrency control algorithm that supports the activation of parallel transactions while preserving a pre-defined commit order; iii) A comprehensive evaluation on two different architectures (message-passing-based and bus-based shared memory in Tilera [103] and x86 respectively).

SMR common ordering layers take multiple communication steps to reach consensus. In SHIELD and by exploiting the local synchronized cycle counter register which is available in all modern multi-core architectures, we developed a low latency ordering layer that supports optimistic delivery. SMR requires determinism in executing clients requests. Each replica executes requests independently and to have the same state all the time, replicas must follow the same order. In SHIELD, we developed a new concurrency control that can execute requests concurrently while preserving the ordering layer requests order. It also support optimistic execution of requests (i.e., speculatively) while the ordering layer is determining the final order.

SoftX. SMR on bus-based shared memory architectures (e.g., x86) showed limited scalabil-

ity and high network delays. SMR requires a high network bandwidth while having a single shared bus represented a bottleneck. This observation motivated us to develop low bandwidth fault tolerant transactional framework (SOFTX). SOFTX is a framework for making a transactional application resilient to transient faults. SOFTX's main goal is preventing data corruption caused by a transient fault from propagating in main memory, without a significant impact on application's performance (i.e.,  $10 \times$  worse). This goal is reached by SOFTX leveraging on speculative processing [84, 83]. When a transaction is activated, SOFTX captures the transaction and forks a number of threads that replicate the execution of the transaction in parallel, speculatively on different cores of the system. We assume an underlying hardware architecture equipped with an enough core count such that the speculative execution does not hamper the application's progress. The outcome of each thread is then compared with the others using dedicated *committer threads*. If it corresponds to the majority outcome, then the transaction can commit and the control is returned to the application. This approach masks transient faults happened during the execution on some core with the speculative execution on other cores.

In SOFTX, computational resources and memory are not partitioned and no ordering protocol is required before to process transactions (e.g., [56, 84]) or after for validating transactions (e.g., [88]). Moreover, hardware cores are reused by other transactions after a commit event; they are not preassigned to certain application threads such that the overall system's load is more balanced.

SOFTX is compatible with both message-passing-based and bus-based shared memory architectures. Its low synchronization bandwidth requirement leverages its performance on bus-based shared memory architectures as well as message-passing-based ones.

To the best of our knowledge, SOFTX is the first attempt to reduce the scope of data corruption to transactional processing without the overhead of classical replication-based solutions. We propose a solution that reduces overhead and increases resources utilization while keeping safety and liveness.

### 1.2 Summary of Proposed Post-Prelim Work

Our post preliminary work will focus on continuing improving best-efforts HTM performance in different situations, not yet explored in the current literature. In this dissertation we started by overcoming HTM resource limitation and then we tackled HTM high contention scenarios by using scheduling. We will continue tackling HTM high contention problem but using a contention manager which does not require a priori knowledge of transactions' working-set. The new proposal works according to online information collected at encounter time. Without static information, the CM increases its accuracy and allows more concurrency. Instead of overestimating all potential accessed objects, actual accesses only are considered based on the current execution of transactions. The real challenge of this proposal is in sharing online information without introducing more aborts due to HTM conflicts. HTM transaction runs speculatively and we cannot know extract information from an aborted transaction as all writes are not available outside the HTM transaction and just discarded after an abort.

As a second future direction we propose to provide nesting supports to HTM. Current Intel HTM implementation supports only flat nesting. We plan to extend HTM nesting support by including closed and open nesting in order to alleviate HTM's flat nesting limitations. Closed nesting improves the performance by increasing the concurrency level [80] and providing a lightweight partial abort mechanism. In fact, with closed nesting when a conflict happens during the execution of a child transaction, only that transaction is aborted and retried, rather than the entire transaction. Open nesting improves the concurrency further [80] because children transactions are allowed to commit their changes to the main memory before the commit of the parent transaction. When the parent transaction is aborted, an undo action is required for compensating children transactions' changes.

We plan to merge all our HTM enhancements and build a comprehensive framework for Hybrid TM algorithms. Hybrid algorithms is gaining more traction as it promises better performance than falling back to global locking. In addition, hybrid TM algorithms shares many building blocks. Our proposed framework makes embedding and testing new hybrid TM algorithms easy. It aims also at helping the research community in developing more hybrid TM algorithms, easily comparing them, and adaptively selecting the best one for a certain situation.

### 1.3 Proposal Outline

The rest of the proposal is organized as follows. Chapter 2 summarize and overview related work. Then we give a background on relevant topics in Chapter 3. PART-HTM details are in Chapter 4 where HTM resource limitations problem is tackled. Chapter 5 describes OCTONAUTS, our HTM-aware scheduler. Then, we move to multi-core dependability in Chapter 6 which describes SHIELD and how we optimized state-machine replication for centralized multi-core architectures. SOFTX and redundant execution details are in Chapter 7. The proposal conclusions and our proposed post-preliminary work are listed in Chapter 8.

## Chapter 2

## **Related Work**

### 2.1 Performance Improvement Using HTM

Research in Hybrid TM (HyTM) [35, 63, 97] started before the recent release of Intel's Haswell processor with HTM support.

PhTM [69] was designed for the Sun's Rock processor, which is a research processor (never been commercially released) that supports HTM. After that, AMD proposed Advanced Synchronization Facility (ASF) [26], which attracted researchers to design the initial Hybrid TM systems [94, 32]. They used ASF support for non-transactional load/store inside HTM transactions to optimize their HyTM proposals. Recently, IBM and Intel released processors with HTM support. On the one hand, IBM's HTM processors are available in Blue Gene/Q and Power8 [18]. On the other hand, Intel released Haswell processors with HTM support.

The release of Haswell processors attracted more research on how to boost Haswell HTM capabilities via software [19, 3, 20, 75, 76, 41, 2]. Haswell is a best-effort HTM and requires a software fall back path. Intel suggested global locking (GL-software path) as a default fall back approach, but, having just one global lock limits parallelism and concurrency. This way, even short transactions are forced to fall back to global locking in high conflict scenarios. This motivated researchers to tackle this problem proposing different approaches.

- Improving the global locking fall back path to increase concurrency [20, 41].

- Using STM as a fall back path in order to reduce conflict between concurrent HTM and STM transactions [94, 32, 19].

- Using reduced hardware transactions where only the STM commit procedure is executed as HTM transaction [76, 75].

More in detail, in [20] authors propose to defer the check of the global lock at the end of an HTM transaction, rather than at the beginning as usual (this process is also called lazy subscription). This approach increases the concurrency but allows HTM transactions to access inconsistent states during the execution. The latter problem is (partially) solved relying on the Haswell HTM sandboxing protection mechanism. In [41], a self-tuning mechanism is proposed to decide the best suited fall back path for an aborted transaction.

In [94, 32], a hybrid version of the NOrec [33] algorithm is proposed. NOrec is an algorithm very suitable for being enriched with HTM supports (hybrid approach) as it uses a single global lock to protect the commit procedure. Optimizing the meta-data shared between HTM and STM is the key point to achieve high performance. Currently, Hybrid NOrec is considered as a state-of-the-art hybrid transactional memory. In [19], a hybrid version of InvalSTM [47] is proposed (Invyswell). Invyswell uses different transaction types: a lightweight HTM, an instrumented HTM, an STM, an irrevocable STM, and a global locking transaction. A transaction moves from one type to another based on the current composition of concurrent transactions and taking into account the contention level.

In [76], reduced hardware transactions (RHT) are introduced. Transactions that fail in hardware are restarted in the slow-path, which consists of an STM transaction that rely on a RHT for accomplishing the commit procedure. If a transaction fails in the slow-path it is finally restarted in slow-slow-path where it execute as plain STM transaction. In [75], the RHT idea is extended to NOrec.

PART-HTM takes a different direction from the above proposals. Instead of falling back to global locking or STM, we partition transactions that fails in hardware due to resource limitations and execute each partition as sub-HTM transaction. We fall back to global locking only when a transaction can never succeed in HTM (e.g., due to hardware interruption or irrevocable operations) or when the contention between transaction is very high.

The problem of partitioning memory operations to fit as a single HTM transaction is described also in [4]. In this approach authors used HTM transactions for concurrent memory reclamation. If the reclamation operation, which involves a linked-list, does not fit in a single HTM transaction, they split it using compiler supports to make the operation suited. PART-HTM differs with [4] because they do not provide a software framework for ensuring consistency and isolation of sub-HTM transactions as we do.

In [3], a similar partitioning approach is used to simulate IBM Power8's rollback-only hardware transaction via Intel Haswell HTM. They solve the opacity problem between hardware transaction and global locking fallback path. The solution is to hide writes that occur in the GL-software path until the end of the critical section without monitoring the reads. They also split the transaction in multiple sub-HTM transactions, and each of them keeps both an undo-log and a redo-log. Before committing, the undo-log is used to restore memory's old values (i.e., hiding the transaction's writes). At the beginning of the next HTM subtransaction, the redo-log is used to restore the previous sub-transaction values. Following this approach, the undo-log and redo-log keep growing from one sub-HTM transaction to the next, consuming an increasing amount of precious HTM resources. As a result, such an approach is not suited for solving the problem of aborts due to resource failures. In fact, the last sub-HTM transaction will still have a write-set that is as big as the original transaction before the splitting process.

## 2.2 Transactional Memory Scheduling

Transactional memory scheduling has been studied extensively in Software Transactional Memory systems [43, 9, 113, 73, 46, 8]. However, TM scheduling for HTM systems has not been explored.

Dragojević et. al. in [46] presented a technique to schedule transactions dynamically based on expected working-sets. In [8], the Steal-On-Abort transaction scheduler is presented. Its idea is to queue aborted transaction behind concurrent conflicting transactions. Thus, prevent them from conflicting again.

Adaptive Transaction Scheduler (ATS) [113] monitors the contention level of the system. When it exceeds a threshold, transactions scheduler takes control. Otherwise, transactions proceeds normally without scheduling.

CAR-STM is presented in [43]. In CAR-STM, each core has its own queue. Potentially conflicting transactions are scheduled on the same core queue to minimize conflicts. In addition, when a transaction is aborted, it is scheduled on the same queue behind the one that conflicted with it. Thus, preventing them from conflicting again in the future.

Proactive Transactional Scheduler (PTS) [14] idea is to proactively schedule transactions before accessing hot spots of the programs. Instead of waiting for transactions to conflict before scheduling them, they are proactively scheduled to reduce contention in the program's hot spots. PTS showed an average of 85% improvement over backoff retry policy in STAMP[21].

In [41], a self-tuning approach for Intel's HTM (Tuner) is presented. The approach is workload-oblivious and does not require any offline analysis or priori knowledge of the program. It uses lightweight profiling techniques. Tuner controls the number of retries in HTM before falling back to global locking. It analyzes a transaction capacity and time to decide the best number of retrials in HTM. This decision is used the next time when the same transaction is executed. If the previous decision does not fit the current run of the transaction, the tuning parameters are reevaluated. Compared to OCTONAUTS, Tuner does not require priori knowledge of the transactions and it is adaptive also. It avoids unnecessary HTM trials for transactions that does not fit in HTM based on its online profiling.

OCTONAUTS is an adaptive scheduler. It is only activated when the contention level is medium to high. It uses a priori knowledge of expected working-set of each transaction to schedule them. Our queues are one per each object. And it allows multiple read-only transactions to proceed concurrently. OCTONAUTS also is HTM-aware scheduler.

## 2.3 Dependability

Many techniques are proposed to handle transient faults that cause data corruption or *silent* data corruption. All techniques are targeting safety where correct results are the main target. But not all of them guarantee liveness.

Checkpointing is a well known technique in High Performance Computing (HPC). The system state is checkpointed periodically and fault detection mechanisms are installed to detect data corruption and restore the system to a correct system state. A major challenge in these system is determining how many checkpoints are required. If the error is detected long time after it occurred, we may have no valid checkpoint to restore. On the other hand, keeping infinite number of checkpoints is not practical. Checkpointing only guarantees safety and has a downtime to restore a checkpoint and re-execute lost requests. Another problem of checkpointing is the time required to checkpoint the system which can be large if the data is huge. [72] has a good survey about checkpointing techniques.

Other approaches in HPC rely on more complex algorithms. They are known as faulttolerant algorithms. Some scientific problems can be modified to support error detection and correction using some encoding mechanisms like checksums. These approaches are algorithm specific and they are difficult to generalize. Encoded processing incurs high processing overhead and requires extra memory. In [72] more information about such techniques can be found.

Some less efficient error detection techniques, in terms of error coverage, are bases on assertions/invariants or symptoms [90]. Assertions are conditions that must exist before and after program state change. Symptoms refer to program activities that are usually related to faults. For example, executing an unknown instruction, and misprediction of a high confidence branch. These techniques do not provide full error coverage. Moreover, these techniques only detect errors and require another mechanism for recovery like checkpointing.

Hardening crash-tolerant systems can tolerate transient faults by using error detection mechanisms. When an error is detected, it is converted to a crash fault by taking the node down. Hardening can be applied to replication-based fault tolerant systems that tolerate crash faults. In this case, it supports both safety and liveness. But it depends on the accuracy of the error detection. Also, error detection must detect faults quickly before they can propagate. PASC [30] is an example of hardening techniques.

Byzantine fault tolerant (BFT) systems can tolerate transient faults by default. When a transient fault occurs, the program can continue its execution (i.e., without crash) while producing incorrect behaviors. But BFT systems have a broader scope as they also target malicious activities (e.g., intrusion). As a result, usually their overhead is high.

Most BFT systems are distributed systems and rely on state-machine replication. In statemachine replication, requests must be totally ordered before execution to guarantee reaching the same state on each replica independently. Each replica executes requests in the same order. Reaching order agreement requires exchanging multiple messages. Some BFT systems execute requests sequentially to guarantee determinism [22, 62]. PBFT [22] is one of the first BFT systems with good performance. It uses batching to improve performance and reduce the number of messages. Zyzzyva [62] reduces the number of messages to the minimum in the gracious execution by using speculation and involving clients in the protocol for detecting faults. Both PBFT and Zyzzyva execute requests sequentially to guarantee determinism. Other BFT systems execute independent requests in parallel to increase system throughput [107, 58, 60]. The key idea is to find independent requests that can run in parallel while forcing dependent requests to run sequentially in the same order in all replicas. In [107], the primary replica executes transactions concurrently. Then a scheduler uses information from primary execution of transactions to drive secondary replicas' execution. It is applicable to 2-phase strict locking systems like some database systems. Eve [58] tries to find independent requests in each batch using a deterministic application-specific mixer. It follows the execute-verify model instead of the agree-on-input model. In [60], operating system transactions of TxOS are used to execute requests and are forced to commit in a predefined order in all replicas. The replica state is limited to kernel-level only. There is no support for general memory transactions or optimistic delivery. In [27], a centralized system is split using isolated virtual machines which represent typical BFT replicas.

Hardware fault-tolerant architectures are more expensive and limited in the number of faults they can tolerate due to the cost of the redundant hardware. For example, NonStop advanced architecture [12] uses two or three replicas. Each replica executes the same instructions stream independently and a voter compares outputs. Hardware resources (memory, disks) are split between replicas and isolated from each other.

SHIELD is software-based and is transparent from the hardware's specification. It is optimized for centralized systems. It uses optimistic delivery combined with transactional execution to achieve high concurrency. Then, it analyzes transaction outcomes and, when a corruption occurs, a restoration is issued.

State-machine replication is a well known paradigm in transaction processing [82, 59]. These works exploit OAB protocols for processing transactions speculatively, overlapping their execution with the coordination time for ordering. They provide resilience to crash/stop failures; in the case of transient faults, data consistency can be corrupted.

Algorithms for processing uncommitted transactions in-order have been proposed in [82, 10]. However, some of them simply ignore the overhead of implementing meta-data forwarding from speculative threads. This overhead can be alleviated in the presence of higher costs like remote communication. In SHIELD, delays are smaller, therefore impacting the overall performance. Thus, SHIELD does not use this technique.

All replication-based fault tolerant systems requires a network with a good bandwidth. All requests are wrapped in a network message and reaching consensus requires some more messages. SOFTX's main goals is to minimize the synchronization overhead. For this reason,

we decided to not wrap transaction requests into network messages and total order them. SOFTX aims for reducing the overhead of the fault-tolerant protocol without partitioning the machine resources between different replicas and without replicating system memory.

Compared to the above techniques, SOFTX is a pure software solution and it inherits both the checkpointing and replication advantages. Using transactional memory to speculatively execute a transaction is similar to taking a checkpoint at the beginning of each transaction. If an error is detected, the execution returns to that checkpoint and retry. SOFTX uses also the same principle of replication by executing the same transaction multiple times in parallel. However, SOFTX's speculative execution is more lightweight: data are not replicated and there is no fixed number of replicas. Thus, synchronization overhead is minimal and cores can be reused by other threads.

SOFTX also supports parallel execution of transactions where multiple thread groups can execute together in the same time. Transactional memory mechanisms coordinate access to shared data. Using dedicated committer threads reduces the synchronization overhead more by minimizing the number of CAS operations. Instead of having all threads competing on the same shared lock, each thread communicates directly with committer threads via a private variable.

Works tackling similar problems (i.e., redundant parallel execution) of SOFTX has been presented in [89, 114]. In [89], authors use relaxed determinism which is similar to relaxed memory consistency model in modern processors. However, developer must insert determinism hints when precise ordering is needed. SOFTX is transparent to the developer. In [114], Delta Execution is presented. It aims for increasing software reliability using multiple, almost redundant, executions. Two almost identical instances run together and split execution only at different code sections. Execution joins again later. Delta Execution requires modifications to the operating system, compiler, and programming language constructs. SOFTX uses transactions which define exactly where parallel speculated execution starts and ends. Moreover, SOFTX is implemented as part of an STM library and requires no changes to the operating system, compiler, and programming language constructs.

Transactional applications are increasingly using Software Transactional Memory (STM) algorithms [100, 34, 104, 42] to overcome the programmability and performance challenges of in-memory processing on multicore architectures.

A locking mechanism based on the idea of executing lock-based critical sections in remote threads has been recently explored in [71, 52]. SOFTX exploits a similar approach using dedicated committer threads for processing transactions' commit phases.

## Chapter 3

## Background

## 3.1 Parallel Programming

Amdahl's law [5] specifies the maximum possible speedup that can be obtained when a sequential program is parallelized. Informally, the law states that, when a sequential program is parallelized, the relationship between the speedup reduction and the sequential part (i.e., sequential execution time) of the parallel program is non-linear. The fundamental conclusion of Amdahl's law is that the sequential fraction of the (parallelized) program has a significant impact on overall performance. Code that must be run sequentially in a parallel program is often due to the need for coordination and synchronization (e.g., shared data structures that must be executed mutual exclusively to avoid race conditions). Per Amdahl's law, this implies that synchronization abstractions have a significant effect on performance.

Lock-based synchronization is the most widely used synchronization abstraction. Coarsegrained locking (e.g., a single lock guarding a critical section) is simple to use, but results in significant sequential execution time: the lock simply forces parallel threads to execute the critical section sequentially, in a one-at-a-time order. With fine-grained locking, a single critical section now becomes multiple shorter critical sections. This reduces the probability that all threads will need the same critical section at the same time, permitting greater concurrency. However, this has low programmability: programmers must acquire only necessary and sufficient locks to obtain maximum concurrency without compromising safety, and must avoid deadlocks when acquiring multiple locks. Moreover, locks can lead to livelocks, lockconvoying, and priority inversion. Perhaps, the most significant limitation of lock-based code is their non-composability. For example, atomically moving an element from one hash table to another using those tables' (lock-based) atomic methods is not possible in a straightforward manner: if the methods internally use locks, a thread cannot simultaneously acquire and hold the locks of the methods (of the two tables); if the methods were to export their locks, that will compromise safety.

### 3.2 Transactional Memory

Transactional Memory (TM) borrows the transaction idea from databases. Database transactions have been successfully used for a long time and have been found to be a powerful and robust concurrency abstraction. Multiple transactions can run concurrently as long as there is no conflict between them. In the case of a conflict, only one transaction among the conflicting ones will proceed and commit its changes, while the others are aborted and retried. TM transactions only access memory, thus they are "memory transactions".

TM can be classified into three categories: Hardware Transactional Memory (HTM), Software Transactional Memory (STM), and Hybrid Transactional Memory (HyTM). HTM [49, 6, 102, 25, 23] uses hardware to support transactional memory operations, usually by modifying cache-coherence protocols. It has the lowest overhead and the best performance. The need for specialized hardware is a limitation. Additionally, HTM transactions are limited in size and time. STM [99, 55, 105, 93, 61, 53, 17, 81, 101, 39] implements all TM functionality in software, and thus can run on any existing hardware and it is more flexible and easier to change. STM's overhead is higher, but with optimizations, it outperforms fine-grained locking and scales well. Moreover, there are no limitations on the transaction size and time. HyTM [70, 68, 91, 36, 79, 111] combines HTM and STM, while avoiding their limitations, by splitting the TM implementation between hardware and software.

#### 3.2.1 TM Design Classification

TM designs can be classified based on four factors: concurrency control, version control, conflict detection, and conflict resolution[50].

#### **Concurrency Control**

A TM system monitors transactions' access to shared data to synchronize between them. A conflict between transactions go through the following events (in that order):

- 1. A conflict *occurs* when two transactions write to the same shared data (write after write), or one transaction writes and the other reads the same shared data (read after write or write after read).

- 2. The conflict is *detected* by the TM system.

- 3. The conflict is *resolved* by the TM system such that each transaction makes progress.

There are two mechanisms for concurrency control: *pessimistic* and *optimistic*. In the pessimistic mechanism, a transaction acquires exclusive access privilege to shared data before

accessing it. When the transaction fails to acquire this privilege, a conflict occurs, which is detected immediately by the TM system. The conflict is resolved by delaying the transaction. These three events occur at the same time.

The pessimistic mechanism is similar to using locks and can lead to deadlocks if it is not implemented correctly. For example, consider a transaction T1 which has access to object D1 and needing access to object D2, while a transaction T2 has access to object D2 and needs access to object D1. Deadlocks such as these can be avoided by forcing a certain order in acquiring exclusive access privileges, or by using timeouts. This mechanism is useful when the application has frequent conflicts. For example, transactions containing I/O operations, which cannot be rolled-back can be supported using this mechanism.

In the optimistic mechanism, conflicts are not detected when it occurs. Instead, they are detected and resolved at any later time or at commit time, but no later than the commit time. During validation, conflicts are detected, and they are resolved by aborting or delaying the transaction.

The optimistic mechanism can lead to livelocks if not implemented correctly. For example, consider a transaction T1 that reads from an object D1, and then a transaction T2 writes to object D1, which forces T1 to abort. When T1 restarts, it may write to D1 causing T2 to abort, and this scenario may continue indefinitely. Livelocks can be solved by using a *Contention Manager*, which waits or aborts a transaction, or delays a transaction's restart. Another solution is to limit a transaction to validate only against committed transactions that were running concurrently with it. The mechanism allows higher concurrency in applications with low number of conflicts. Also, it has lower overhead since its implementation is simpler.

This approach is also know as *deferred updates*.

#### **Conflict Detection**

TM systems use different approaches for when and how a conflict is detected. There are two approaches for when a conflict is detected: *eager* conflict detection and *lazy* conflict detection [79]. In eager conflict detection, the conflict is detected at the time it happens. At each access to the shared data (read or write), the system checks whether it causes a conflict.

In lazy conflict detection, a conflict is detected at commit time. All read and written locations are validated to determine if another transaction has modified them. Usually this approach validates during transactions' life times or at every read. Early validations are useful in reducing the amount of wasted work and in detecting/preventing *zombie* transactions (i.e., a transaction that gets into an inconsistent state because of an invalid read, which may cause it to run forever and never commit).

## 3.3 Intel's HTM

The current Intel's HTM implementation of Haswell processor, also called Intel Haswell Restricted Transactional Memory (RTM) [92], is a best-effort HTM, namely no transaction is guaranteed to eventually commit. In particular, it enforces space and time limitations. Haswell's RTM uses L1 cache (32KB) as a transactional buffer for read and write operations. Accessed cache-lines are marked as "monitored" whenever accessed. HTM synchronization management is embedded into the cache coherence protocol. The eviction and invalidation of cache lines defines when a transaction is aborted (it reproduces the idea of read-set and write-set invalidation of STM).

This way, the cache-line size is indeed the granularity used for detecting conflicts. When two transactions need the same cache-line and at least one wants to write it, an abort occurs. When this happens, the application is notified and the transaction can restart as HTM or can fall back to a software path. The transaction that detects the data conflict will abort. The detection of a conflict is based on how the cache coherence protocol works. We cannot know exactly which thread will detect the conflict as the details of Intel's cache coherence protocol are not publicly available.

In addition to those aborts due to data conflict, HTM transactions can be aborted for other reasons. Any cache-line eviction due to cache depletion or associativity causes the transaction to abort, which means that hardware transactions are limited in space by the size of the L1 cache for its write-set. For a transaction's read-set, Intel's HTM implementation can go beyond the L1 cache capacity using a special hardware reads buffer [29]. For the read-set, the value of the read operation is not required for validation as conflicts can be detected by the object's memory address only. Thus, a cache line eviction from the read-set does not always abort the transaction. Also, any hardware interrupt, including the interrupt from timer, force HTM transactions to abort.

Cache associativity places another limitation on transactional size. Intel's Haswell L1 cache has an associativity of 8. Thus, some transactions accessing just 9 different locations that are mapped to the same L1 cache set (due to associativity mapping rules) will be aborted. In addition, when Hyper-Threading is enabled, L1 cache is shared between the two logical cores on the same physical core.

Intel's HTM programming model is based on three new instructions: \_xbegin; \_xend, and \_xabort. \_xbegin is used to start a transaction. All operations following the execution of \_xbegin are transactional and speculative. If a transaction is aborted due to a conflict, transactional resource limitation, unsupported instruction (e.g., CPUID) or explicit abort, then all updates done by the transaction are discarded and the processor returns to non-transactional mode. \_xend is used to finish and commit a transaction. \_xabort is used to explicitly abort a transaction.

When a transaction is aborted (implicitly or explicitly), the program control jump to the

Figure 3.1: Relation between number of components on the same chip and soft-errors rate. (Figure from [11])

abort handler and the abort reason is provided in the EAX register. The abort reason let the programmer know whether the transaction is aborted due to conflict, limited transactional resources, debug breakpoint, or explicit abort. In addition, an integer value can be passed from \_xabort to the abort handler.

A programmer must provide a software fallback path to guarantee progress. For example, a transaction that faces a page fault interrupt, can never commit in HTM. It will be aborted every time when the interrupt is fired. In addition, the interrupt will not handled as the transaction is running speculatively.

### 3.4 Soft-errors

Soft-errors [16, 11] are transient faults that may happen anytime during application execution. They are caused by physical phenomena [11], e.g., cosmic particle strikes or electric noise, which cannot be directly managed by application designers or administrators. As a result, when a soft-error occurs, the hardware is not affected by interruption, but applications may crash or behave incorrectly. A soft error can cause a single bit in a CPU register to flip (i.e., residual charge inverting the state of a transistor). Most of the time, such an event is likely to be unnoticed by applications because they do not use that value (e.g., unused register). However, sometimes, the register can contain an instruction pointer or a memory pointer. In those cases, the application behavior can be unexpected.

Figure 3.2: Relation between transistor size and soft-errors rate. (Figure from [16])

Figure 3.1 shows an example on the relation of the number of components on the same chip and the soft-errors rate. As the number of the components increases, the soft-error increases. Multi-core architectures are getting more cores on the same chip and the number of transistors is doubled approximately every two years.

Figure 3.2 shows the relation of the transistor size and the soft-errors rate. As the transistor size gets smaller, the rate of soft-errors increase. Currently, Intel uses 22nm manufacturing technology and it is expected to move 16nm technology with the next generation of processors.

#### **3.5** Fault tolerance techniques

In this section, we will go through a number of fault tolerance solution that focus on transient faults including silent data corruption.

#### 3.5.1 Checkpointing

Checkpointing [72] means taking a snapshot of the system state periodically while the system is correct. The system is monitored by a failure detector, which signals when the system is faulty (e.g., detect data corruption). When a fault is detected, the system state is restored to latest correct checkpoint. From the time when the fault is detected until completing the checkpoint restoration, the system is unreachable. Transient faults represents a challenge for the checkpointing recovery mechanism. The symptom of a transient fault do not appear instantaneously, whereas the transient fault could be detected only after a period of time, which cannot be bound. Thus, the system has to keep a number of checkpoints that covers an arbitrary period of time. Another issue with transient faults is how to distinguish between a correct checkpoint from a faulty checkpoint. Usually a transient fault is detected by its symptoms and it is difficult to identify the source of the transient fault.

#### 3.5.2 Encoding

Some algorithms can be enforced by encoding in software [72]. For example, an additional operation can be encoded such that the result indicates whether an error occurred or not. In hardware, encoding is widely used to detect and correct faults. For example, memory modules equipped with Error-Correcting Code (ECC) can detect and correct errors in the memory module. Based on the encoding technique used, an error can be only detected or also fixed. In addition, the number of detectable/correctable errors is limited.

#### 3.5.3 Assertions/Invariants

This technique [90] can detect faults only without recovery. It is based on monitoring the system for unexpected behaviors (e.g., a change in an invariant). The error's coverage for this technique is however very limited. An assertion is added after each change to the program state to detect faults during that operation. Invariants refer to the program expected behavior, e.g., executing an unknown instruction or a misprediction of a high confidence branch.

#### 3.5.4 Replication

Replicating the system state on multiple isolated replica guarantees full error recovery in case of a replica is hit by a fault. State-machine replication (SMR) is a famous replication technique which is used by many replication fault-tolerant systems (e.g., Byzantine fault tolerant (BFT)). In SMR, request are executed by each replica independently. In order to reach the same final state on each replica, replicas have to execute requests in the same order. Thus, a consensus must be reached on the requests order between all replicas. Based on the fault model, a consensus technique can tolerate permanent faults (e.g., crash) only (e.g., Paxos [65]) or the consensus technique can tolerate malicious behavior also (e.g., the three generals problem [66]).

For permanent faults, one replica response is enough to tolerate a permanent fault. On the other hand, transient and malicious faults requires voting and having a majority to tolerate

a transient fault. Permanent faults consensus requires 2f + 1 replicas to tolerate f faults, while Byzantine faults consensus requires 3f + 1 replicas to tolerate f faults. Byzantine fault voting requires only 2f + 1 replicas to tolerate f faults [112].

## Chapter 4

## Part-HTM

### 4.1 Problem Statement